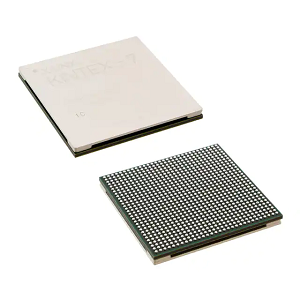

XC7K420T-2FFG901I – Porowhita Whakakotahitia, Whakamaua, Nga Huanga Kuaha Ka taea te Papatono

Huanga Hua

| MOMO | WHAKAAHUA |

| kāwai | Takiwa Whakakotahi (ICs)Kua mau Huanga Huanga Kuaha Whakatakataka (FPGA) |

| kaihanga | AMD |

| raupapa | Kintex®-7 |

| takai | paepae |

| Te mana hua | Hohe |

| Ka taea e DigiKey te hōtaka | Kaore i manatoko |

| LAB/CLB nama | 32575 |

| Te maha o nga huānga arorau/waewae | 416960 |

| Te maha o nga moka RAM | 30781440 |

| Te maha o nga I/Os | 380 |

| Ngaohiko - Tuku hiko | 0.97V ~ 1.03V |

| Momo whakaurunga | Momo whakapiri mata |

| Te pāmahana whakahaere | -40°C ~ 100°C (TJ) |

| Mōkī/Whare | 900-BBGA, FCBGA |

| Te whakaurunga o nga waahanga kaihoko | 901-FCBGA (31x31) |

| Tau ariki hua | XC7K420 |

| MOMO | WHAKAAHUA |

| kāwai | Takiwa Whakakotahi (ICs)Kua mau |

| kaihanga | AMD |

| raupapa | Kintex®-7 |

| takai | paepae |

| Te mana hua | Hohe |

| Ka taea e DigiKey te hōtaka | Kaore i manatoko |

| LAB/CLB nama | 32575 |

| Te maha o nga huānga arorau/waewae | 416960 |

| Te maha o nga moka RAM | 30781440 |

| Te maha o nga I/Os | 380 |

| Ngaohiko - Tuku hiko | 0.97V ~ 1.03V |

| Momo whakaurunga | Momo whakapiri mata |

| Te pāmahana whakahaere | -40°C ~ 100°C (TJ) |

| Mōkī/Whare | 900-BBGA, FCBGA |

| Te whakaurunga o nga waahanga kaihoko | 901-FCBGA (31x31) |

| Tau ariki hua | XC7K420 |

Nga FPGA

Nga painga

Ko nga painga o nga FPGA e whai ake nei:

(1) Kei roto i nga FPGA nga rauemi taputapu penei i nga pūtau arorau, te RAM, te whakarea, me era atu. Ma te whakarite tika i enei rauemi taputapu, ka taea te whakatinana i nga iahiko taputapu penei i te whakarea, te rehita, te whakaputa korero, me etahi atu.

(2) Ka taea te hoahoa FPGA ma te whakamahi i nga hoahoa poraka, i te Verilog HDL ranei, mai i nga iahiko kuaha ngawari ki nga iahiko FIR, FFT ranei.

(3) Ko nga FPGA ka taea te whakahoahoa mo te kore mutunga, ka utaina he otinga hoahoa hou i roto noa i nga rau manomano, ma te whirihora ano hei whakaiti i nga taputapu o runga.

(4) Ko te auau whakahaere o te FPGA e whakatauhia ana e te maramara FPGA me te hoahoa, ka taea te whakarereke, te whakakapi ranei ki te maramara tere ake ki te whakatutuki i etahi whakaritenga e hiahiatia ana (ahakoa, ko te tikanga, ko te auau whakahaere kaore i te mutunga ka taea. kia piki ake, engari ka whakahaerehia e nga tikanga IC o naianei me etahi atu mea).

Nga huakore

Ko nga ngoikoretanga o nga FPGA e whai ake nei:

(1) Ka whakawhirinaki nga FPGA ki te whakatinana taputapu mo nga mahi katoa kaore e taea te whakatinana i nga mahi penei i te peke herenga.

(2) Ka taea e nga FPGA anake te whakatinana i nga mahi-waahi.

Hei whakarāpopototanga: Ka whakawhirinaki nga FPGA ki nga taputapu ki te whakatinana i nga mahi katoa, ka taea te whakataurite ki nga maramara kua whakatapua i runga i te tere, engari he nui te waahi i roto i te ngawari o te hoahoa ki te whakataurite ki nga kaihanga kaupapa whanui.

Nga reo hoahoa me nga papaaho

Ko nga taputapu arorau ka taea te whakarite he kaikawe taputapu e hangai ana i nga mahi kua whakaritea me nga whakaritenga hangarau o nga tono hiko ma te hangarau EDA.Ko nga FPGA, ko tetahi o nga taputapu auraki e whakatinana ana i tenei huarahi, he mea tika ki te kaiwhakamahi, he tino ngawari me te whai kiko, he ngawari ki te whakamahi, he tere ki te whakamatautau me te whakatinana i nga taputapu.

Ko te Reo Whakaahua Maamaa (HDL) he reo e whakamahia ana ki te hoahoa i nga punaha arorau matihiko me te whakaahua iahiko matihiko, ko nga mea matua e whakamahia nuitia ana ko VHDL, Verilog HDL, System Verilog me te Pūnaha C.

Hei reo whakaahuatanga taputapu huri noa, ko te Tino High Speed Integrated Circuit Hardware Description Language (VHDL) kei a ia nga ahuatanga o te noho motuhake mai i te iahiko taputapu motuhake me te motuhake o te papahoa hoahoa, me nga painga o te kaha o te whakamaarama whanui, kaore. ti'aturi i runga i nga taputapu motuhake, me te kaha ki te whakaahua i te hoahoa o te arorau mana matatini i roto i te waehere pakari me te poto, me etahi atu e tautokohia ana e te maha o nga kamupene EDA, kua whakamahia nuitia i roto i te waahanga o te hoahoa hiko.whakamahia whānuitia.

Ko te VHDL he reo taumata teitei mo te hoahoa ara iahiko, a ka whakatauritea ki etahi atu reo whakaahuatanga taputapu, kei a ia nga ahuatanga o te reo ngawari, te ngawari me te motuhake mai i te hoahoa taputapu, ka waiho hei reo whakaahuatanga taputapu noa mo te hangarau EDA me te hanga hangarau EDA ake. e waatea ana ki nga kaihoahoa.

Ko te Verilog HDL he reo whakaahuatanga taputapu e whakamahia nuitia ana ka taea te whakamahi i nga waahanga maha o te mahinga hoahoa taputapu, tae atu ki te whakatauira, te whakahiato me te whaihanga.

Verilog HDL Painga: he rite ki te C, ngawari ki te ako me te ngawari.Pū-tairongo.He pai ki te tuhi whakaihiihi me te whakatauira.Nga ngoikoretanga: he maha nga hapa kaore e kitea i te wa whakahiato.

VHDL AtAKi: He wetereo pakari, he maamaa te naakapa.Nga ngoikoretanga: te wa whakamohiotanga roa, kaore i te ngawari.

Ko te rorohiko Quartus_II he taiao hoahoa papa-maha kua oti te hanga e Altera, ka taea e ia te whakatutuki i nga hiahia hoahoa o nga momo FPGA me nga CPLD, a he taiao matawhānui mo te hoahoa punaha-a-kiripi ka taea te whakamahere.

Vivado Design Suite, he taiao hoahoa whakauru i tukuna e te kaihoko FPGA Xilinx i te tau 2012. Kei roto he taiao hoahoa tino whakauru me te reanga hou o nga taputapu mai i te punaha ki te taumata IC, i hangaia katoa i runga i te tauira raraunga tauineine tiritahi me te taiao patuiro noa.ko te Xilinx Vivado Design Suite e whakarato ana i nga kohanga IP FIFO ka taea te whakamahi ngawari ki nga hoahoa.